Innovazioni nella Litografia: Superare le Sfide con la Co-ottimizzazione Maschera-Wafer

All’interno del progresso tecnologico dei chip semiconduttori si nasconde una sfida cruciale: ridurre le dimensioni e aumentare l’efficienza dei componenti elettronici. Questa problematica è particolarmente rilevante nel campo della litografia, un processo che permette di creare schemi complessi sui materiali semiconduttori, noti come wafer, per la produzione di chip. La litografia impiega un tipo di modello, chiamato fotomaschera o semplicemente maschera, per generare questi schemi sui wafer. L’industria è costantemente alla ricerca di metodi che migliorino la risoluzione e la producibilità sia delle maschere che dei wafer, al fine di ottenere chip più veloci e con una maggiore resa di chip funzionanti.

Le tecniche di litografia computazionale, che migliorano la risoluzione e la fedeltà dei modelli, come la correzione della prossimità ottica (OPC), hanno compiuto passi da gigante nell’affrontare queste sfide, modificando i modelli individuali delle maschere per ottimizzare la stampa sia delle maschere che dei wafer. La tecnologia di litografia inversa (ILT) — un approccio matematicamente rigoroso che definisce le forme delle maschere per ottenere i risultati desiderati sui wafer — è considerata una soluzione promettente per superare le difficoltà della litografia per chip avanzati. Da quando è stata introdotta più di un decennio fa, numerosi studi hanno dimostrato che le forme delle maschere ILT curvilinee producono i migliori risultati sui wafer.

Tuttavia, fino a un passato recente, i tempi di esecuzione associati a questa tecnica computazionale ne hanno limitato l’applicazione pratica ai punti critici dei chip. Nel 2019, è stato proposto un sistema completamente nuovo, progettato appositamente, che include un approccio accelerato da GPU in grado di simulare una coppia unica GPU/CPU gigante, capace di computare una soluzione ILT completa per l’intero chip in una volta sola. Questo approccio innovativo, progettato sistematicamente per l’ILT e l’accelerazione GPU, ha reso la ILT a chip completo una realtà pratica nella produzione.

Questo metodo si basava sulla scrittura di maschere multi-fascio, un’importante novità nel campo della scrittura di maschere che, essendo basata sui pixel, è agnostica in termini di tempo di scrittura rispetto alla forma. Rimaneva da vedere se i benefici dell’ILT curvilineo a chip completo potessero essere estesi ai writer di maschere a fascio variabile (VSB), che scrivono forme rettilinee (e talvolta triangolari) anziché pixel, e che costituiscono la maggioranza dei writer di maschere nel mondo oggi. Mentre i writer VSB creano rapidamente forme rettangolari più grandi scrivendo un rettangolo per volta, i modelli di maschere complesse possono rappresentare una sfida poiché il numero elevato di piccoli rettangoli richiesti per crearli richiederebbe troppo tempo per essere scritto.

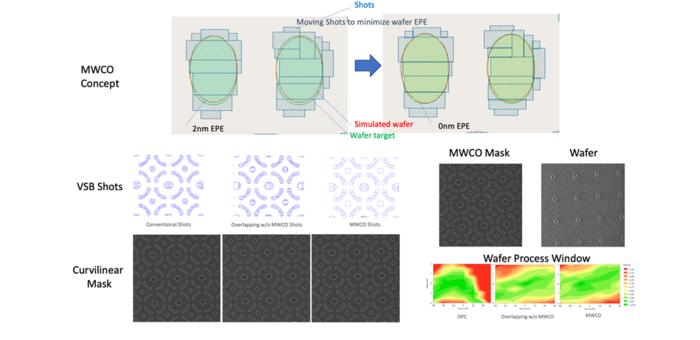

Nel loro lavoro pubblicato sulla rivista Journal of Micro/Nanopatterning, Materials, and Metrology, il team di D2S, Inc. ha inventato un metodo chiamato co-ottimizzazione maschera-wafer (MWCO) con tre intuizioni: sia il writer di maschere che lo scanner wafer funzionano come filtri passa-basso; sovrapporre gli scatti guidati dalla simulazione maschera/wafer può creare forme curvilinee con meno scatti; puntando al modello wafer, anziché al modello di maschera, si possono creare scatti molto più semplici per stampare il corretto modello wafer. Utilizzando questa doppia simulazione, la qualità di stampa del wafer viene ottimizzata iterativamente mentre si manipolano i bordi degli scatti VSB per produrre forme di maschere rettilinee target note per essere scrivibili su un writer VSB, con un conteggio di scatti noto e accettabile.

D2S e Micron Technology hanno dimostrato che MWCO può ridurre la variazione del wafer di 3 volte e migliorare la finestra di processo del wafer di 2 volte rispetto all’OPC di Micron, indicando un miglioramento sostanziale nella precisione e affidabilità del processo di litografia. Il tempo di scrittura per una maschera ILT curvilinea completa sarebbe inferiore a 12 ore, soddisfacendo i requisiti di produzione ad alto volume.

Questo significa che tutti i produttori di semiconduttori ora possono produrre chip non solo più piccoli, ma anche con prestazioni superiori e minor consumo energetico, anche se non dispongono di un writer di maschere multi-fascio.

Configurazioni di tiro VSB e relativi modelli sulla maschera.

Maschera MWCO e relativa stampa wafer.

Wafer Process Windows mostra la finestra di processo MWCO migliorata di 2 volte.

La finestra di processo è una misura chiave della qualità di stampa dei wafer.

CREDITO

Gli autori doi 10.1117/1.JMM.23.1.011207.